Heterogeneous Computing

| High-Performance Artificial Intelligence | HW Proto + Tooling | TRL Levels: 3-5 | Linked WPs: 1, 5, 7 | UC: Autonomous Driving |

| CPS Efficient deployment of Artificial Intelligence and Image Processing Applications | ||||

| High-Complexity Autonomous CPS (robots, vehicles, drones) | Potential market entry: Q4 2023 | Re-engineering effort: 24 hm | ||

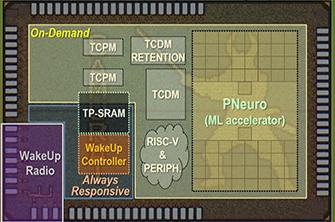

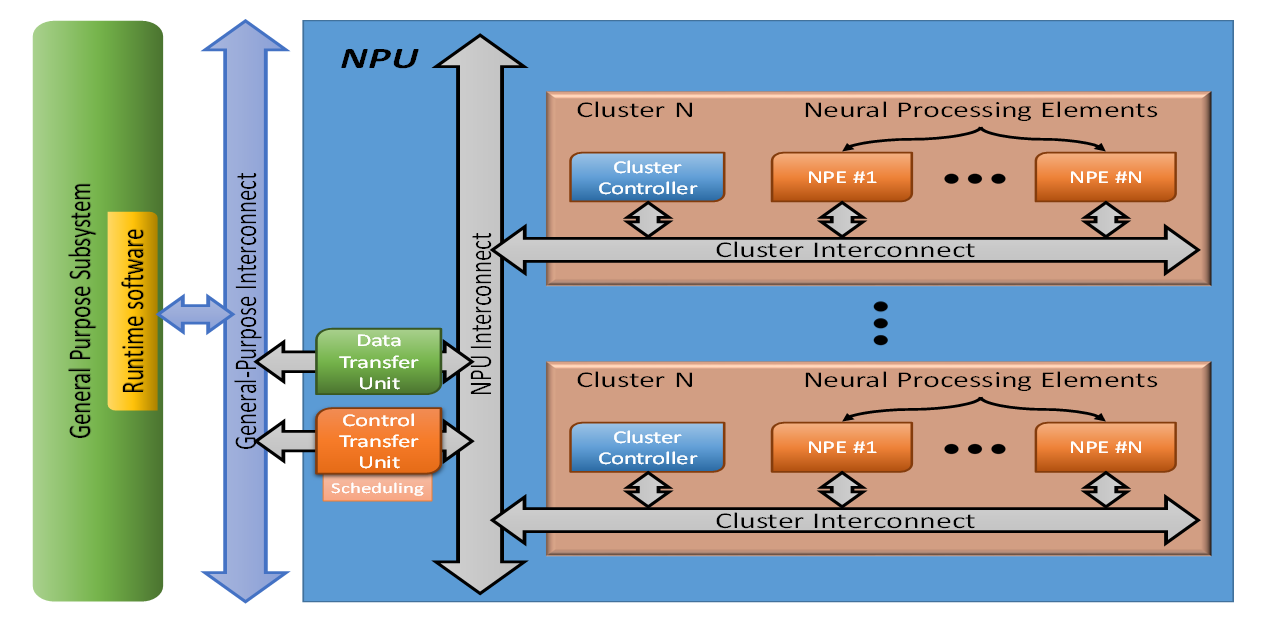

| The Heterogeneous Computing PIARCH includes two contributions: – A research prototype neural networks hardware accelerator – A methodology to design and deploy efficient neural network solutions. The hardware accelerator is the neural processing unit (NPU). This specialized hardware accelerator is designed with 3 objectives in minds: dedication to neural network based algorithms, low power consumption and high performance. The methodology is designed to help developers of NN-based algorithms to port and optimize their software to a wide variety of hardware accelerators.

|

|

|||